# Lab-Report Analogue Electronics

Staircase Generator

Name:Dirk BeckerCourse:BEng 2Group:AStudent No.:9801351Date:05/May/1999

# 1. Contents

| 1. | CONTENTS                | .2 |

|----|-------------------------|----|

| 2. | INTRODUCTION            | .3 |

| 3. | THE STAIRCASE GENERATOR | .3 |

| a) | Astable A               | 4  |

| b) | Astable B               | 6  |

| c) | The Integrator          | 8  |

| 4. | THE MEASURED STAIRCASE  | .9 |

| 5. | CONCLUSION              | .9 |

# **<u>2. Introduction</u>**

Analogue devices such as Opamps and Timers are often used in combination with transistors to generate or form signals.

These circuits are usually not very complex and can produce relatively exact signals. Here a Staircase generator was to built up.

# 3. The Staircase Generator

The staircase generator used in the Lab was copied from the IEE Engineering Science and Education Journal, Vol. 8, No. 1, February 1999, pages 25-26.

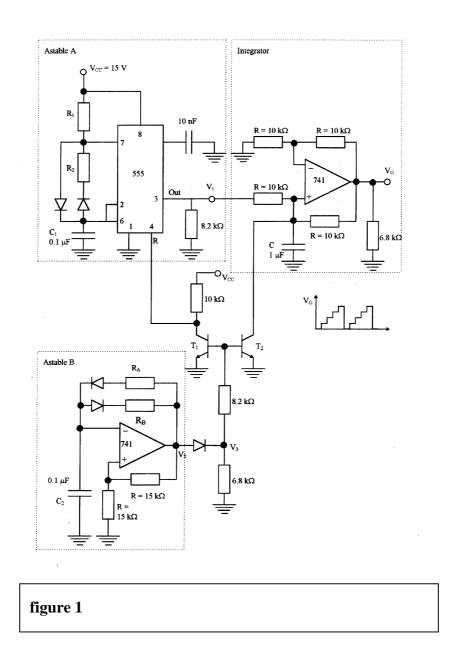

Figure 1 shows the circuit diagram of the staircase generator, where the Astable A generates the frequency of stairs and Astable B generates the frequency of the staircases. The Integrator increases the output voltage bit for bit by integrating the impulses from Astable A and generates by this way the increasing staircase. When the impulses arrive, the output voltage of the Integrator increases rapidly and holds, when no impulses are applied. Transistor T2 resets the Astable A (Timer NE555), discharges the capacitor C and a new staircase begins. The reset impulses are generated by Astable B and determine the overall frequency of the Staircases, where the width of the different stairs is determined by Astable A.

#### a) Astable A

The Astable A is realised with an NE555 timer IC. It generates the impulses of the stairs, which must be of an exact duration.

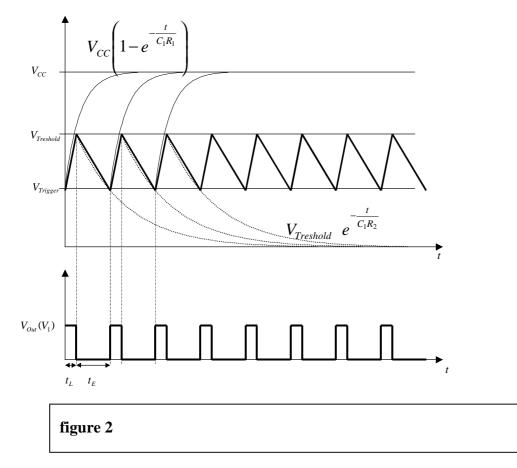

Figure 2 shows how the Astable with the Timer NE55 works. The  $0.1\mu$ F capacitor is charged through R<sub>1</sub> and discharged through R<sub>2</sub> and Pin 7 (Discharge Input of NE555). The two diodes prevent the resistors from influence of each other (Exact duty times). When the voltage at the capacitor increases the threshold voltage of the NE555 (2/3 V<sub>CC</sub>), the output switched to 0V until the capacitor voltage decreases the trigger voltage at Pin 2 (1/3 V<sub>CC</sub>).

#### Equations for NE555:

Charge: R1, Diode, C1  $\tau_{charge} = 6.5k\Omega * 0.1\mu F = 0.65 ms$

discharge: C1, Diode, R2

$\tau_{_{disch\,arg\,e}}=41k\Omega*0.1\mu F=4.1~ms$

$$\begin{aligned} V_c &= (V_{CC} - V_D)^* \left( 1 - e^{-\frac{t}{\tau_{charge}}} \right) \\ \Rightarrow & t_1 = -\tau_{charge}^* \ln \left( 1 - \frac{V_{C1}}{V_{CC} - V_D} \right) = -0.65ms^* \ln \left( 1 - \frac{10V}{15V - 0.7V} \right) \\ \hline t_1 &= 0.7781 \, ms \\ \Rightarrow & t_2 = -\tau_{charge}^* \ln \left( 1 - \frac{V_{C2}}{V_{CC} - V_D} \right) = -0.65ms^* \ln \left( 1 - \frac{5V}{15V - 0.7V} \right) \\ \hline t_2 &= 0.28 \, ms \end{aligned}$$

discharge:

$$V_{c} = (V_{C1} - V_{D}) * e^{-\frac{t}{\tau_{discharge}}}$$

$$\Rightarrow t_{discharge} = -\tau_{discharge} * \ln\left(\frac{V_{C2}}{V_{C1} - V_{D}}\right) = -4.1ms * \ln\left(\frac{5V}{10V - 0.7V}\right)$$

$$t_{discharge} = 2.54 ms$$

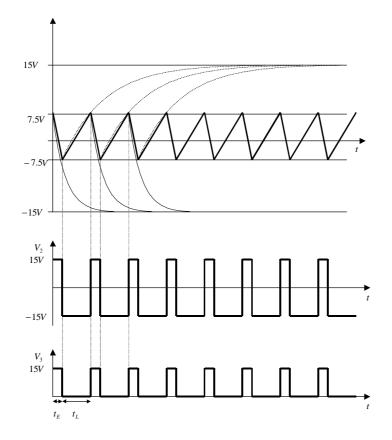

#### b) Astable B

The Astable B works in a similar way than the other one. The  $0.1\mu$ F capacitor is charged through  $R_A$  and discharged through  $R_B$ . When increasing or decreasing the positive or negative voltage at the + input of the LM741, the 741 switches to the opposite state (Comparator mode). The diode at the output suppresses the negative parts of the output voltage.

#### Equations for LM741:

Charge: R1, Diode, C1

$\tau_{ch \arg e} = 6.5 k\Omega * 0.1 \mu F = 0.65 \ ms$

discharge: C1, Diode, R2

$$\tau_{discharg_e} = 41k\Omega * 0.1\mu F = 4.1 \, ms$$

$$V_c = (V_{CC} - V_D) * \left( 1 - e^{-\frac{t}{\tau_{ch \arg e}}} \right)$$

$$\Rightarrow t_1 = -\tau_{charg_e} * \ln\left(1 - \frac{V_{C1}}{V_{CC} - V_D}\right) = -0.65ms * \ln\left(1 - \frac{10V}{15V - 0.7V}\right)$$

$$t_1 = 0.7781 ms$$

$$\Rightarrow t_2 = -\tau_{charg_e} * \ln\left(1 - \frac{V_{C2}}{V_{CC} - V_D}\right) = -0.65ms * \ln\left(1 - \frac{5V}{15V - 0.7V}\right)$$

$$t_2 = 0.28 ms$$

$$\Rightarrow t_{charg_e} = t_1 - t_2 = 0.502 ms$$

discharge:

$$V_{c} = (V_{C1} - V_{D}) * e^{-\frac{t}{\tau_{discharge}}}$$

$$\Rightarrow t_{discharge} = -\tau_{discharge} * \ln\left(\frac{V_{C2}}{V_{C1} - V_{D}}\right) = -4.1ms * \ln\left(\frac{5V}{10V - 0.7V}\right)$$

$$t_{discharge} = 2.54 ms$$

#### c) The Integrator

The integrator part has to sum the incoming impulses from Astable A and to amplify and buffer them. The advantage of the used integrator is, that it is a non-inverting amplifier. It consists of a lowpass filter (R=10k $\Omega$  and v=1 $\mu$ F) and an LM741. The capacitor can be discharged via T2 to begin a new staircase signal. Also Transistor T1 is switched on, in order to reset the NE555 and synchronise the stairs (start stairs, when complete staircase starts).

$$i_i + i_0 - i_e = 0$$

$$\Rightarrow \quad \frac{V_0 - V_t}{R} + \frac{V_i - V_t}{R} - C \frac{dV_p}{dt} = 0$$

with  $V_0 = 2V_p = 2V_n$

$$V_0 - \frac{V_0}{2} + V_i - \frac{V_0}{2} - CR \frac{dV_p}{dt} = 0$$

$$\Rightarrow \frac{1}{RC}V_i = \frac{dV_p}{dt}$$

$$V_p = \frac{1}{RC}\int_0^t V_i \, dt + k$$

with

$$k = V_i(0)$$

$$\Rightarrow V_0 = \frac{2}{RC} \int_0^t V_i \, dt + V_0(0)$$

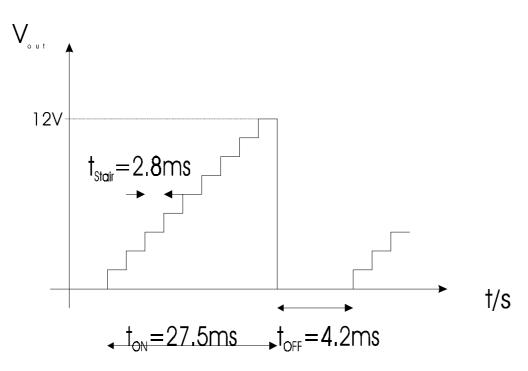

### 4. The measured staircase

The measured values are close to the calculated. some differences come from the non ideal resistors and capacitors, which had not all their desired values (+- 5per cent).

The voltage of each staircase was about 0.6V - 1V.

## 5. Conclusion

Very useful circuits can be built up with simple analogue devices. The lab assignment showed the superposition of three different circuits which where connected together for obtaining an appropriate result. Major problem of analogue circuits is the inaccuracy of the different components, which all add their errors and can result incorrect signals.